In computing, signed number representations are required to encode negative numbers in binary number systems.

In mathematics, negative numbers in any base are represented by prefixing them with a minus sign ('−'). However, in computer hardware, numbers are represented only as sequences of bits, without extra symbols. The four best-known methods of extending the binary numeral system to represent signed numbers are: sign-and-magnitude, ones' complement, two's complement, and offset binary. Some of the alternative methods use implicit instead of explicit signs, such as negative binary, using the base −2. Corresponding methods can be devised for other bases, whether positive, negative, fractional, or other elaborations on such themes.

There is no definitive criterion by which any of the representations is universally superior. For integers, the representation used in most current computing devices is two's complement, although the Unisys ClearPath Dorado series mainframes use ones' complement.

History[edit]

The early days of digital computing were marked by a lot of competing ideas about both hardware technology and mathematics technology (numbering systems). One of the great debates was the format of negative numbers, with some of the era's most expert people having very strong and different opinions.[citation needed] One camp supported two's complement, the system that is dominant today. Another camp supported ones' complement, where any positive value is made into its negative equivalent by inverting all of the bits in a word. A third group supported 'sign & magnitude' (sign-magnitude), where a value is changed from positive to negative simply by toggling the word's sign (high-order) bit.

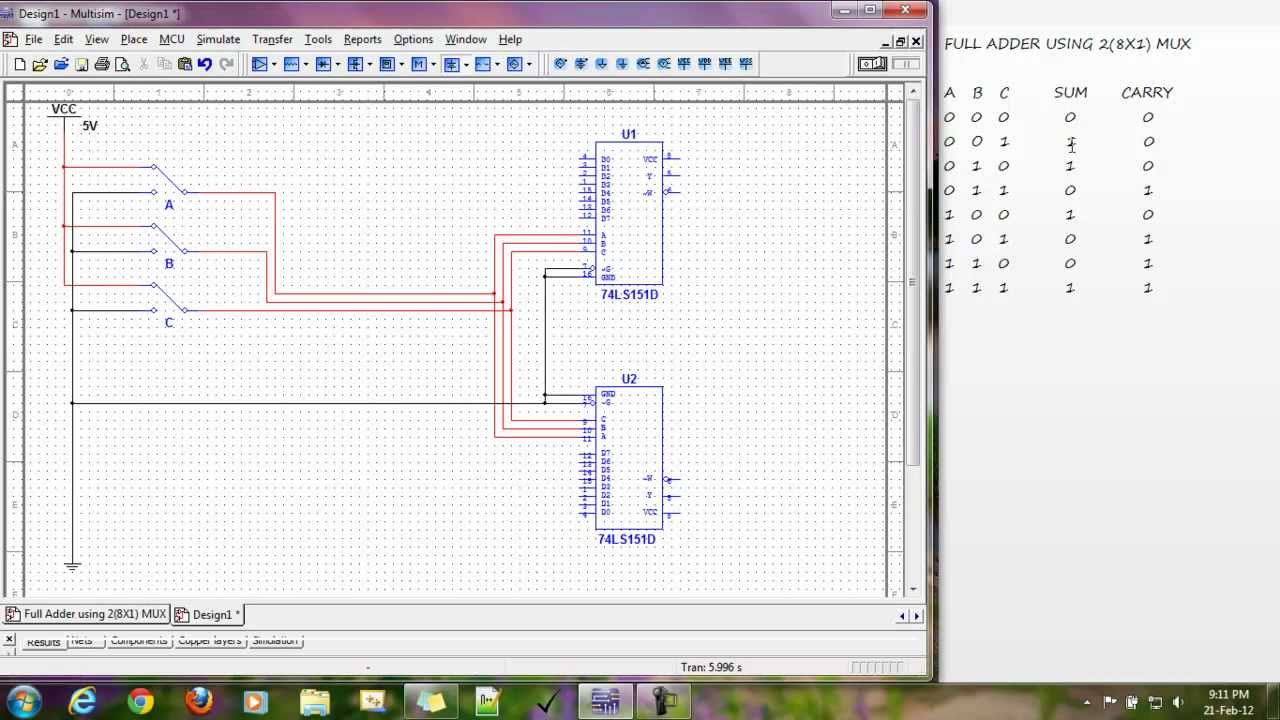

CS61C Summer 2018 Lab 5 - Introduction to Logisim. Launch the Logisim Evolution application to begin. Place logic gates and other circuits to make Out2 to be the negative 'sign and magnitude' value of the input. Sign and magnitude is an alternate way of representing signed values - like 2s complement, but simpler!

There were arguments for and against each of the systems. Sign & magnitude allowed for easier tracing of memory dumps (a common process in the 1960s) as small numeric values use fewer 1 bits. Internally, these systems did ones' complement math so numbers would have to be converted to ones' complement values when they were transmitted from a register to the math unit and then converted back to sign-magnitude when the result was transmitted back to the register. The electronics required more gates than the other systems – a key concern when the cost and packaging of discrete transistors were critical. IBM was one of the early supporters of sign-magnitude, with their 704, 709 and 709x series computers being perhaps the best-known systems to use it.

Ones' complement allowed for somewhat simpler hardware designs as there was no need to convert values when passed to and from the math unit. But it also shared an undesirable characteristic with sign-magnitude – the ability to represent negative zero (−0). Negative zero behaves exactly like positive zero; when used as an operand in any calculation, the result will be the same whether an operand is positive or negative zero. The disadvantage, however, is that the existence of two forms of the same value necessitates two rather than a single comparison when checking for equality with zero. Ones' complement subtraction can also result in an end-around borrow (described below). It can be argued that this makes the addition/subtraction logic more complicated or that it makes it simpler as a subtraction requires simply inverting the bits of the second operand as it is passed to the adder. The PDP-1, CDC 160 series, CDC 3000 series, CDC 6000 series, UNIVAC 1100 series, and the LINC computer use ones' complement representation.

Two's complement is the easiest to implement in hardware, which may be the ultimate reason for its widespread popularity.[1] Processors on the early mainframes often consisted of thousands of transistors – eliminating a significant number of transistors was a significant cost savings. Mainframes such as the IBM System/360, the GE-600 series,[2] and the PDP-6 and PDP-10 use two's complement, as did minicomputers such as the PDP-5 and PDP-8 and the PDP-11 and VAX. The architects of the early integrated circuit-based CPUs (Intel 8080, etc.) chose to use two's complement math. As IC technology advanced, virtually all adopted two's complement technology. x86,[3]m68k, Power ISA,[4]MIPS, SPARC, ARM, Itanium, PA-RISC, and DEC Alpha processors are all two's complement.

Signed magnitude representation[edit]

This representation is also called 'sign–magnitude' or 'sign and magnitude' representation. In this approach, a number's sign is represented with a sign bit: setting that bit (often the most significant bit) to 0 for a positive number or positive zero, and setting it to 1 for a negative number or negative zero. The remaining bits in the number indicate the magnitude (or absolute value). For example, in an eight-bit byte, only seven bits represent the magnitude, which can range from 0000000 (0) to 1111111 (127). Thus numbers ranging from −12710 to +12710 can be represented once the sign bit (the eighth bit) is added. For example, −4310 encoded in an eight-bit byte is 10101011 while 4310 is 00101011. Using signed magnitude representation has multiple consequences which makes them more intricate to implement:[5]

- There are two ways to represent zero, 00000000 (0) and 10000000 (−0).

- Addition and subtraction require different behaviour depending on the sign bit, whereas one's complement can ignore the sign bit and just do an end-around carry, and two's complement can ignore the sign bit and depend on the overflow behavior.

- Comparison also require inspecting the sign bit, whereas in two's complement, one can simply subtract the two numbers, and check if the outcome is positive or negative.

- The minimum negative number is −127 instead of −128 in the case of two's complement.

This approach is directly comparable to the common way of showing a sign (placing a '+' or '−' next to the number's magnitude). Some early binary computers (e.g., IBM 7090) use this representation, perhaps because of its natural relation to common usage. Signed magnitude is the most common way of representing the significand in floating-point values.

Ones' complement[edit]

| Binary value | Ones' complement interpretation | Unsigned interpretation |

|---|---|---|

| 00000000 | +0 | 0 |

| 00000001 | 1 | 1 |

| ⋮ | ⋮ | ⋮ |

| 01111101 | 125 | 125 |

| 01111110 | 126 | 126 |

| 01111111 | 127 | 127 |

| 10000000 | −127 | 128 |

| 10000001 | −126 | 129 |

| 10000010 | −125 | 130 |

| ⋮ | ⋮ | ⋮ |

| 11111101 | −2 | 253 |

| 11111110 | −1 | 254 |

| 11111111 | −0 | 255 |

Alternatively, a system known as ones' complement[6] can be used to represent negative numbers. The ones' complement form of a negative binary number is the bitwise NOT applied to it, i.e. the 'complement' of its positive counterpart. Like sign-and-magnitude representation, ones' complement has two representations of 0: 00000000 (+0) and 11111111 (−0).[7]

As an example, the ones' complement form of 00101011 (4310) becomes 11010100 (−4310). The range of signed numbers using ones' complement is represented by −(2N−1 − 1) to (2N−1 − 1) and ±0. A conventional eight-bit byte is −12710 to +12710 with zero being either 00000000 (+0) or 11111111 (−0).

To add two numbers represented in this system, one does a conventional binary addition, but it is then necessary to do an end-around carry: that is, add any resulting carry back into the resulting sum.[8] To see why this is necessary, consider the following example showing the case of the addition of −1 (11111110) to +2 (00000010):

In the previous example, the first binary addition gives 00000000, which is incorrect. The correct result (00000001) only appears when the carry is added back in.

A remark on terminology: The system is referred to as 'ones' complement' because the negation of a positive value x (represented as the bitwise NOT of x) can also be formed by subtracting x from the ones' complement representation of zero that is a long sequence of ones (−0). Two's complement arithmetic, on the other hand, forms the negation of x by subtracting x from a single large power of two that is congruent to +0.[9] Therefore, ones' complement and two's complement representations of the same negative value will differ by one.

Note that the ones' complement representation of a negative number can be obtained from the sign-magnitude representation merely by bitwise complementing the magnitude.

Two's complement[edit]

| Binary value | Two's complement interpretation | Unsigned interpretation |

|---|---|---|

| 00000000 | 0 | 0 |

| 00000001 | 1 | 1 |

| ⋮ | ⋮ | ⋮ |

| 01111110 | 126 | 126 |

| 01111111 | 127 | 127 |

| 10000000 | −128 | 128 |

| 10000001 | −127 | 129 |

| 10000010 | −126 | 130 |

| ⋮ | ⋮ | ⋮ |

| 11111110 | −2 | 254 |

| 11111111 | −1 | 255 |

The problems of multiple representations of 0 and the need for the end-around carry are circumvented by a system called two's complement. In two's complement, negative numbers are represented by the bit pattern which is one greater (in an unsigned sense) than the ones' complement of the positive value.

In two's-complement, there is only one zero, represented as 00000000. Negating a number (whether negative or positive) is done by inverting all the bits and then adding one to that result.[10] This actually reflects the ring structure on all integers modulo2N: . Addition of a pair of two's-complement integers is the same as addition of a pair of unsigned numbers (except for detection of overflow, if that is done); the same is true for subtraction and even for N lowest significant bits of a product (value of multiplication). For instance, a two's-complement addition of 127 and −128 gives the same binary bit pattern as an unsigned addition of 127 and 128, as can be seen from the 8-bit two's complement table.

An easier method to get the negation of a number in two's complement is as follows:

| Example 1 | Example 2 | |

|---|---|---|

| 1. Starting from the right, find the first '1' | 00101001 | 00101100 |

| 2. Invert all of the bits to the left of that '1' | 11010111 | 11010100 |

Method two:

- Invert all the bits through the number

- Add one

Example: for +2, which is 00000010 in binary (the ~ character is the Cbitwise NOT operator, so ~X means 'invert all the bits in X'):

- ~00000010 → 11111101

- 11111101 + 1 → 11111110 (−2 in two's complement)

Offset binary[edit]

| Binary value | Excess-128 interpretation | Unsigned interpretation |

|---|---|---|

| 00000000 | −128 | 0 |

| 00000001 | −127 | 1 |

| ⋮ | ⋮ | ⋮ |

| 01111111 | −1 | 127 |

| 10000000 | 0 | 128 |

| 10000001 | 1 | 129 |

| ⋮ | ⋮ | ⋮ |

| 11111111 | +127 | 255 |

Offset binary, also called excess-K or biased representation, uses a pre-specified number K as a biasing value. A value is represented by the unsigned number which is K greater than the intended value. Thus 0 is represented by K, and −K is represented by the all-zeros bit pattern. This can be seen as a slight modification and generalization of the aforementioned two's-complement, which is virtually the excess-(2N−1) representation with negatedmost significant bit.

Biased representations are now primarily used for the exponent of floating-point numbers. The IEEE 754 floating-point standard defines the exponent field of a single-precision (32-bit) number as an 8-bit excess-127 field. The double-precision (64-bit) exponent field is an 11-bit excess-1023 field; see exponent bias. It also had use for binary-coded decimal numbers as excess-3.

Base −2[edit]

In conventional binary number systems, the base, or radix, is 2; thus the rightmost bit represents 20, the next bit represents 21, the next bit 22, and so on. However, a binary number system with base −2 is also possible.The rightmost bit represents (−2)0 = +1, the next bit represents (−2)1 = −2, the next bit (−2)2 = +4 and so on, with alternating sign. The numbers that can be represented with four bits are shown in the comparison table below.

The range of numbers that can be represented is asymmetric. If the word has an even number of bits, the magnitude of the largest negative number that can be represented is twice as large as the largest positive number that can be represented, and vice versa if the word has an odd number of bits.

Comparison table[edit]

The following table shows the positive and negative integers that can be represented using four bits.

| Decimal | Unsigned | Sign and magnitude | Ones' complement | Two's complement | Excess-8 (biased) | Base −2 |

|---|---|---|---|---|---|---|

| +16 | N/A | N/A | N/A | N/A | N/A | N/A |

| +15 | 1111 | N/A | N/A | N/A | N/A | N/A |

| +14 | 1110 | N/A | N/A | N/A | N/A | N/A |

| +13 | 1101 | N/A | N/A | N/A | N/A | N/A |

| +12 | 1100 | N/A | N/A | N/A | N/A | N/A |

| +11 | 1011 | N/A | N/A | N/A | N/A | N/A |

| +10 | 1010 | N/A | N/A | N/A | N/A | N/A |

| +9 | 1001 | N/A | N/A | N/A | N/A | N/A |

| +8 | 1000 | N/A | N/A | N/A | N/A | N/A |

| +7 | 0111 | 0111 | 0111 | 0111 | 1111 | N/A |

| +6 | 0110 | 0110 | 0110 | 0110 | 1110 | N/A |

| +5 | 0101 | 0101 | 0101 | 0101 | 1101 | 0101 |

| +4 | 0100 | 0100 | 0100 | 0100 | 1100 | 0100 |

| +3 | 0011 | 0011 | 0011 | 0011 | 1011 | 0111 |

| +2 | 0010 | 0010 | 0010 | 0010 | 1010 | 0110 |

| +1 | 0001 | 0001 | 0001 | 0001 | 1001 | 0001 |

| +0 | 0000 | 0000 | 0000 | 0000 | 1000 | 0000 |

| −0 | 1000 | 1111 | ||||

| −1 | N/A | 1001 | 1110 | 1111 | 0111 | 0011 |

| −2 | N/A | 1010 | 1101 | 1110 | 0110 | 0010 |

| −3 | N/A | 1011 | 1100 | 1101 | 0101 | 1101 |

| −4 | N/A | 1100 | 1011 | 1100 | 0100 | 1100 |

| −5 | N/A | 1101 | 1010 | 1011 | 0011 | 1111 |

| −6 | N/A | 1110 | 1001 | 1010 | 0010 | 1110 |

| −7 | N/A | 1111 | 1000 | 1001 | 0001 | 1001 |

| −8 | N/A | N/A | N/A | 1000 | 0000 | 1000 |

| −9 | N/A | N/A | N/A | N/A | N/A | 1011 |

| −10 | N/A | N/A | N/A | N/A | N/A | 1010 |

| −11 | N/A | N/A | N/A | N/A | N/A | N/A |

Same table, as viewed from 'given these binary bits, what is the number as interpreted by the representation system':

| Binary | Unsigned | Sign and magnitude | Ones' complement | Two's complement | Excess-8 | Base −2 |

|---|---|---|---|---|---|---|

| 0000 | 0 | 0 | 0 | 0 | −8 | 0 |

| 0001 | 1 | 1 | 1 | 1 | −7 | 1 |

| 0010 | 2 | 2 | 2 | 2 | −6 | −2 |

| 0011 | 3 | 3 | 3 | 3 | −5 | −1 |

| 0100 | 4 | 4 | 4 | 4 | −4 | 4 |

| 0101 | 5 | 5 | 5 | 5 | −3 | 5 |

| 0110 | 6 | 6 | 6 | 6 | −2 | 2 |

| 0111 | 7 | 7 | 7 | 7 | −1 | 3 |

| 1000 | 8 | −0 | −7 | −8 | 0 | −8 |

| 1001 | 9 | −1 | −6 | −7 | 1 | −7 |

| 1010 | 10 | −2 | −5 | −6 | 2 | −10 |

| 1011 | 11 | −3 | −4 | −5 | 3 | −9 |

| 1100 | 12 | −4 | −3 | −4 | 4 | −4 |

| 1101 | 13 | −5 | −2 | −3 | 5 | −3 |

| 1110 | 14 | −6 | −1 | −2 | 6 | −6 |

| 1111 | 15 | −7 | −0 | −1 | 7 | −5 |

Other systems[edit]

Google's Protocol Buffers 'zig-zag encoding' is a system similar to sign-and-magnitude, but uses the least significant bit to represent the sign and has a single representation of zero. This allows a variable-length quantity encoding intended for nonnegative (unsigned) integers to be used efficiently for signed integers.[11]

Another approach is to give each digit a sign, yielding the signed-digit representation. For instance, in 1726, John Colson advocated reducing expressions to 'small numbers', numerals 1, 2, 3, 4, and 5. In 1840, Augustin Cauchy also expressed preference for such modified decimal numbers to reduce errors in computation.

See also[edit]

References[edit]

- ^Choo, Hunsoo; Muhammad, K.; Roy, K. (February 2003). 'Two's complement computation sharing multiplier and its applications to high performance DFE'. IEEE Transactions on Signal Processing. 51 (2): 458–469. doi:10.1109/TSP.2002.806984.

- ^GE-625 / 635 Programming Reference Manual. General Electric. January 1966. Retrieved August 15, 2013.

- ^Intel 64 and IA-32 Architectures Software Developer’s Manual(PDF). Intel. Section 4.2.1. Retrieved August 6, 2013.

- ^Power ISA Version 2.07. Power.org. Section 1.4. Retrieved August 6, 2013.,

- ^Bacon, Jason W. (2010–2011). 'Computer Science 315 Lecture Notes'. Retrieved 21 February 2020.

- ^US 4484301, 'Array multiplier operating in one's complement format', issued 1981-03-10

- ^US 6760440, 'One's complement cryptographic combiner', issued 1999-12-11

- ^Shedletsky, John J. (1977). 'Comment on the Sequential and Indeterminate Behavior of an End-Around-Carry Adder'(PDF). IEEE Transactions on Computers. 26 (3): 271–272. doi:10.1109/TC.1977.1674817.

- ^Donald Knuth: The Art of Computer Programming, Volume 2: Seminumerical Algorithms, chapter 4.1

- ^Thomas Finley (April 2000). 'Two's Complement'. Cornell University. Retrieved 15 September 2015.

- ^Protocol Buffers: Signed Integers

- Ivan Flores, The Logic of Computer Arithmetic, Prentice-Hall (1963)

- Israel Koren, Computer Arithmetic Algorithms, A.K. Peters (2002), ISBN1-56881-160-8

TTL-7447-like implementation for logisim

The 7-segment display driver is an implementation of or BCD (Binary Coded Decimal) to 7-segment display decoder and driver.

It allows you to send binary numbers to a 7 segment display rather than implementing every character yourself.

What is Logisim ?

Logisim is a circuit simulator. More info: http://www.cburch.com/logisim/

We would recommend using. Coreldraw technical suite 2019 crack. CAN NOT DOWNLOAD: Some probably encounter the following error: This site can’t be reached.sundryfiles.com’s server IP address could not be found. In this case, please use and you will get rid of trouble. If downloaded file can not be extracted (file corrupted.), please make sure you have downloaded the file completely and don't use Winzip, it sucks!

How to use ?

Step 1

First of all you will need to download the this project (link), or clone.

Then create a new circuit pressing 'CTRL + N'.

See:

Step 2

Right click at your circuit folder, go to 'Load Library' > 'Logisim Library' then find the '7-segment-display-drive.circ' file

Step 3

After loading the library, you need to add the component to your circuit.

It's easy to see down in the list, the component:

Step 4

Make your circuit, and remember the display pins are:

So, after connecting the Driver to the display, your circuit should look like this:

Examples

Inside the examples folder, you can see some circuits:

Example 1 - Switch

Example 2 - Flip Flop JK (Async)

Docs

Here you can see the Truth table, that I used to make the circuit:

| Hex | D | C | B | A | a | b | c | d | e | f | g |

|---|---|---|---|---|---|---|---|---|---|---|---|

| 0 | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 0 |

| 1 | 0 | 0 | 0 | 1 | 0 | 1 | 1 | 0 | 0 | 0 | 0 |

| 2 | 0 | 0 | 1 | 0 | 1 | 1 | 0 | 1 | 1 | 0 | 1 |

| 3 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 0 | 1 |

| 4 | 0 | 1 | 0 | 0 | 0 | 1 | 1 | 0 | 0 | 1 | 1 |

| 5 | 0 | 1 | 0 | 1 | 1 | 0 | 1 | 1 | 0 | 1 | 1 |

| 6 | 0 | 1 | 1 | 0 | 1 | 0 | 1 | 1 | 1 | 1 | 1 |

| 7 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 0 | 0 | 0 |

| 8 | 1 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

| 9 | 1 | 0 | 0 | 1 | 1 | 1 | 1 | 0 | 0 | 1 | 1 |

| A | 1 | 0 | 1 | 0 | 1 | 1 | 1 | 0 | 1 | 1 | 1 |

| B | 1 | 0 | 1 | 1 | 0 | 0 | 1 | 1 | 1 | 1 | 1 |

| C | 1 | 1 | 0 | 0 | 1 | 0 | 0 | 1 | 1 | 1 | 0 |

| D | 1 | 1 | 0 | 1 | 0 | 1 | 1 | 1 | 1 | 0 | 1 |

| E | 1 | 1 | 1 | 0 | 1 | 0 | 0 | 1 | 1 | 1 | 1 |

| F | 1 | 1 | 1 | 1 | 1 | 0 | 0 | 0 | 1 | 1 | 1 |